June 22 -25, 2025

Moscone Center West | San Francisco, CA

**SPONSORED BY**

IN TECHNICAL COOPERATION WITH

**DIAMOND EVENT SPONSOR**

### DEAR COLLEAGUES,

Welcome to the 62nd DAC, the Chips to Systems Conference, where we come together to shape the next generation of electronics!

We're thrilled to welcome you to San Francisco, California, one of the world's most beautiful cities and a global hub for high-tech innovation. For this week, San Francisco becomes the design and design automation capital of the world! There's so much for you across the three vibrant floors of the Moscone West Convention Center.

DAC is unique in bringing together industry and academic researchers, designers, developers, vendors, and training partners under one roof. It's the premier venue for both learning and networking — opportunities that go well beyond the technical sessions. Join us for evening networking and poster sessions on Sunday, Monday, and Tuesday. This year, we're also offering twice-daily coffee breaks on both the exhibition and research floors, along with snack bars to keep you energized throughout the day.

Now in its 62nd year, DAC continues to lead the world in design and design automation, spanning everything from chips to complete systems. This year, our five core themes—Design, EDA, Systems, AI, and Security—are closely aligned with key technology trends such as Low Power, Chiplets, Cloud, and Security. These themes also reflect pressing industrial needs like Aerospace & Defense, Automotive, Consumer Electronics, Data Centers, and Industrial Systems.

Thanks to the dedication of countless volunteers, the DAC Executive Committee has assembled a dynamic four-day program packed with top-tier research sessions, expert design forums, and a robust exhibition.

This year's DAC features three inspiring keynotes, offering perspectives from both industry and academia on semiconductors, AI, and EDA. You also won't want to miss our SKYtalks, TechTalks, and Analyst Reviews—covering cutting-edge technologies, systems, applications, and trends shaping the future.

Our Research Track showcases 420 accepted papers across 30 tracks, selected from a record-breaking 1,862 submissions — a 20% increase over last year. The program also includes seven Special Sessions featuring invited presentations from leading experts. Five Tutorials and six Workshops on Sunday will offer additional training and hands-on learning opportunities. Be sure to check out the Late-Breaking Results and Work-in-Progress poster sessions for a preview of emerging directions in the field.

Complementing this is the vibrant Engineering Track, tailored for chip designers and technical managers. With strong focus areas including Front-End design, Back-End design, IP, AI, Systems and Software, and Chiplets. This year's submissions reflect continued growth with over 5.8% increase from the previous year. The track also includes special sessions and panels led by prominent industry experts and executives.

As always, exhibit floor remains a hub of excitement, with over 120 exhibitors and 25 first-time exhibitors. There are three Pavilions to experience:

- DAC Pavilion on Level 2 Experience the very forefront of innovation.

- Exhibitor Forum on Level 1 Get first-hand information on new tools and methodologies.

- **EE Times Chiplet Pavilion on Level 2** Explore sessions and exhibitors focused on the design and implementation of Chiplets.

For a quick bite to eat or a beverage, visit the **Grab 'n Go Concession Area at the back of the 1600 Aisle on Level 1.** And don't forget that DAC is hosting a **Career Development Day** for early career and student attendees on Tuesday from 10:00 AM – 3:30 PM just inside the Level 1 exhibit hall.

To ensure you don't miss a moment, download the DAC Mobile App — it's your best tool for planning your schedule, navigating all three levels of Moscone West, and staying updated throughout the week.

I look forward to seeing and speaking with many of you in San Francisco, June 22–25. Together, let's LEARN TODAY and CREATE TOMORROW.

Enjoy the DAC 62!

**HELEN LI**62nd DAC General Chair

### **TABLE OF CONTENTS**

| Conference Information      |

|-----------------------------|

| DAC Directory Maps          |

| In Memoriam                 |

| Networking Receptions       |

| Keynotes Presentations10    |

| SKYTalk Presentations13     |

| TechTalk Presentations      |

| Analyst Presentations       |

| DAC Awards and Scholarships |

| DAC Pavilion Schedule       |

| Exhbitor Forum              |

| Technical Program           |

| Sunday                      |

| Monday                      |

| Tuesday69                   |

| Wednesday95                 |

| Additional Meetings         |

| I LOVE DAC                  |

| Industry Sponsorships118    |

| Exhibitor List119           |

| Committees 122              |

### CONFERENCE INFORMATION

#### **Exhibit Hours**

#### **Location: First and Second Floor**

Monday

10:00 AM - 6:00 PM

Tuesday

10:00 AM - 6:00 PM

Wednesday

10:00 AM - 4:00 PM

#### **Registration Hours**

#### **Location: Level 1 Lobby**

Saturday

12:00 PM - 5:00 PM

Sunday

7:00 AM - 7:00 PM

Monday

7:00 AM - 7:00 PM

Tuesday

7:00 AM - 6:00 PM

Wednesday

7:00 AM - 1:00 PM

#### **Online Proceedings**

To view the proceedings, please visit – <a href="https://www.dac.com/proceedings62">https://www.dac.com/proceedings62</a>

#### Stay Connected

Enjoy complimentary WiFi at DAC:

Wifi Network: DAC2025

Wifi Password: 62DAC2025

#### First Aid Room

Moscone West First Aid Office is located on the 1st Floor, near the Howard Street entrance (behind registration).

Phone: 415.974.4159

REPORT ALL MEDICAL EMERGENCIES IMMEDIATELY

To report a medical emergency, call 511 on a white house

phone, or on a call phone dial 415.974.4021.

#### **DAC Mobile App**

You can download the official conference mobile app in the following ways:

- Search your device's App Store for "DAC Conferences"

- Go to the following link: <a href="https://www.core-apps.com/dl/62dac">https://www.core-apps.com/dl/62dac</a>

- Once the DAC Conferences application has downloaded, choose "62nd DAC"

- Select to download the event app

Once you are in the app don't forget to set up your profile by going to the Publish My Profile icon. If you click the box to publish your profile your name (and picture if you upload one) will show in the Attendee icon. From there you can make "Friendships" with other attendees which will allow you to send messages, and set up private appointments.

For technical assistance please contact <a href="mailto:support@core-apps.com">support@core-apps.com</a>

### **DAC DIRECTORY MAP: LEVEL 1**

MINNA STREET

SHUTTLE BUS ZONE - HOWARD STREET

### **LEVEL 1 EXHIBIT FLOOR**

**Exhibits: Aisles 1200 - 1700**

**DAC Grab 'n Go Concession**

**Exhibitor Forum**

2026 Exhibit Sales Office

**Community Connection Zone**

Career Development Day

(Tuesday, June 24)

### **LEVEL 1 LOBBY**

Registration

# FOURTH STREET

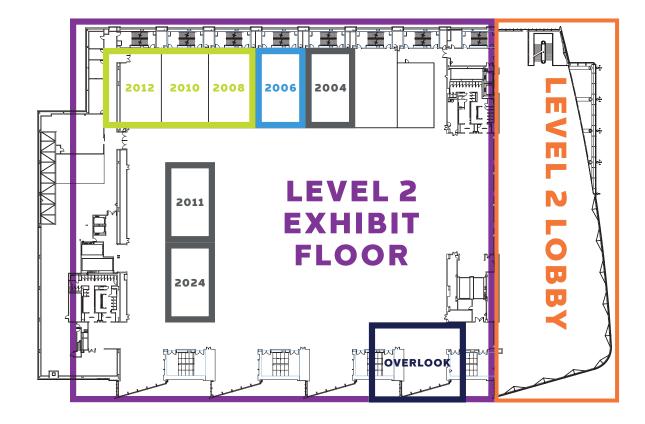

### **DAC DIRECTORY MAP: LEVEL 2**

MINNA STREET

**HOWARD STREET**

ROOMS 2004, 2011, 2024

**Exhibitor Meeting Rooms**

**ROOM 2006**

FIFTH STREET

**Hands-on Training Sessions**

**ROOMS 2008 - 2012**

**Engineering Track Sessions**

LEVEL 2 EXHIBIT FLOOR

**Exhibits: Aisles 2100 - 2600**

**DAC Pavilion**

**EE Times Chiplet Pavilion Engineering Track Posters**

#### LEVEL 2 LOBBY

**Networking Receptions**

Work-in-Progress & Late Breaking Results Posters

**HACK @ DAC**

**PhD Forum & University Demo**

**Young Fellows Posters**

**OVERLOOK**

**Press Room**

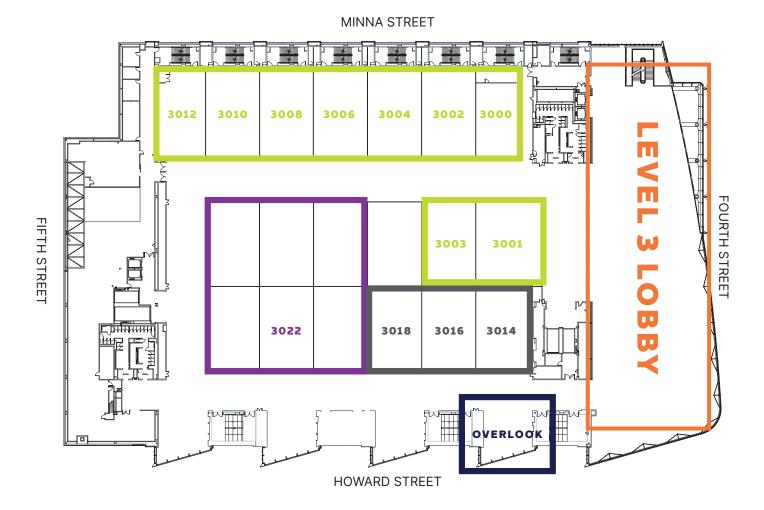

#### DAC DIRECTORY MAP: LEVEL 3

## ROOMS 3000-3004, 3006, 3008, 3010, 3012

**Research Sessions**

**Birds of a Feather**

**Panel Sessions**

**Special Sessions**

**Workshops & Tutorials**

### ROOMS 3014, 3016, 3018

**Exhibitor/Sponsor Meeting Rooms**

IEEE Council on EDA Distinguished Panel (Tuesday, June 24)

### **ROOM 3022**

**Keynote (Monday-Wednesday)**

### LEVEL 3 LOBBY

Welcome Reception (Sunday, June 22)

Work-in-Progress Posters (Sunday, June 22)

**Speaker Breakfast**

**TPC Reception**

### **OVERLOOK**

**Speaker Ready Room**

#### IN MEMORIAM

James Boddie, DSP Pioneer (February 1950 – December 2, 2024)

Jim devoted his long career to expanding the world of digital signal processing. His early work in developing signal-processing algorithms on minicomputers with attached array processors led him to cutting-edge signal-processing research at Bell Labs. That work resulted in the development of the DSP1, which AT&T successfully deployed in the 5ESS electronic switch. After the DSP1 project, he held a variety of positions at Bell Labs, AT&T Microelectronics, Lucent

Technologies, Agere Systems, and finally StarCore, where he directed the development of increasingly powerful DSP chips.

**Robert (Bob) K. Brayton**, Professor Emeritus, University of California at Berkeley (October 1933 – January 10, 2025)

Robert K. Brayton, Professor Emeritus of the Electrical Engineering and Computer Sciences Department at the University of California, Berkeley, was a pioneer in logic synthesis and formal verification. With a career spanning over six decades, he made groundbreaking contributions to

the field of electronic design automation, authoring over 450 technical papers and 10 books. For the first 26 years of his career, he was a member of the Mathematical Sciences Department at IBM's T.J. Watson Research Center, where he led the Yorktown Silicon Compiler team. His work there helped create one of the most advanced logic synthesis systems of its time. His contributions earned him numerous accolades, including the IEEE CAS Technical Achievement Award and the Phil Kaufman Award. Professor Brayton was known for his inquisitive mind, collaborative spirit, and dedication to mentoring students. His legacy continues to inspire future generations of engineers and researchers. He will be deeply missed by his colleagues, students, and the broader academic community.

**Derek Chiou,** Professor, University of Texas at Austin (February 1968 – December 26, 2024)

Derek was a frequent contributor / attendee to DAC. He joined the faculty at the University of Texas, Austin (UT), and worked at Microsoft as a Partner Hardware Architect. In 2020, he returned to UT as a full professor and was honored with the Temple Foundation Endowed

Teaching Fellowship in Engineering.

**Professor Hidetoshi Onodera,** Professor Emeritus of Kyoto University, Japan (December 1955 – October 7, 2024)

Hidetoshi Onodera contributed to the EDA field for many years and was an active participant in CEDA. He was Program Chair of ASP-DAC11, General Chair of ASP-DAC12, and SC Chair of ASP-DAC20 through ASP-DAC26.

### DAC NETWORKING OPPORTUNITIES

### **Networking Receptions**

#### Sunday, June 22

**Welcome Reception & Work-in-Progress Session**

6:00 PM - 7:00 PM | Level 3 Lobby

#### Monday, June 23

**Engineering Track Poster Session**

5:00 PM - 6:00 PM | Level 2 Exhibit Hall

Women in Tech Reception, & Work-in-Progress/Late Breaking Results Poster Session

6:00 PM - 7:00 PM | Level 2 Lobby

#### Tuesday, June 24

Engineering Track Poster Session

5:00 PM - 6:00 PM | Level 2 Exhibit Hall

**Networking Reception**

6:00 PM - 7:00 PM | Level 2 Lobby

#### Wednesday, June 25

**Engineering Track Poster Session**12:15 PM – 1:15 PM | Level 2 Exhibit Hall

## IEEE COUNCIL ON EDA DISTINGUISHED PANEL - 20TH ANNIVERSARY PANEL

#### Al Hardware & EDA, the next 20 years: Smarter, Taller, Deeper

**Date:** Tuesday, June 24 | **Time:** 12:00 PM – 1:30 PM | **Location:** 3016/3018, 3rd Floor

**Panelist**

ALBERTO SANGIOVANNI-VINCENTELLI

EDGAR L. AND HAROLD H. BUTTNER CHAIR OF EECS, UC BERKELEY

Moderator

SUBHASISH MITRA

WILLIAM E. AYER PROFESSOR OF EE AND CS, STANFORD UNIVERSITY

Moderator

L. MIGUEL SILVEIRA

PRO-RECTOR U LISBOA, PROFESSOR OF ECE, IST TECNICO LISBOA

**Panelist**

**KUNLE OLUKOTUN**

CADENCE DESIGN PROFESSOR OF EE AND CS, STANFORD UNIVERSITY, CO-FOUNDER AND CHIEF TECHNOLOGIST, SAMBANOVA SYSTEMS

Panelist

VAMSI BOPPANA

SENIOR VP AI, AMD

### **KEYNOTE PRESENTATIONS**

WILLIAM CHAPPELL

VP OF MISSION SYSTEMS, MICROSOFT

## The Evolution of Innovation: The Dawn of Reasoning Agents in Chip Design

Monday, June 23 | 8:45 AM - 10:00 AM

The Design Automation Conference (DAC) has long been a beacon for technological foresight and innovation in the semiconductor industry. As we look beyond 2025, the landscape of chip design is poised for another transformative leap with the advent of reasoning agents. This evolution builds upon the foundational milestones set by the Electronics Resurgence Initiative (ERI), which revitalized U.S. semiconductor research, and the integration of cloud computing for silicon. The emergence of Generative AI (GenAI) heralds a new era of creativity and efficiency in design processes across multiple domains.

In this keynote, we will explore how reasoning agents are set to revolutionize the semiconductor industry by offering unprecedented capabilities in problem-solving and decision-making. These agents, drawing inspiration from scientific methodologies in other domains, promise to enhance the precision and speed of design, automate manual tasks, while also fostering a collaborative environment between human designers and Al systems. We will delve into the practical applications of these agents, showcasing their potential to streamline complex design challenges, drive innovation, and increase productivity.

The DAC continues to play a crucial role in this journey, serving as a platform for sharing insights, fostering collaboration, and setting the stage for the next wave of technological advancements. By embracing the synergy between AI and human expertise, we are not only shaping the future of microelectronics but also redefining the boundaries of what is possible in chip design. Join us as we navigate this exciting frontier and explore the opportunities that lie ahead.

**ABOUT:** Dr. William Chappell is the Vice President and CTO for the Strategic Missions and Technologies Division at Microsoft. As CTO for SMT, he works across the quantum, 5G, mission, space and federal teams to infuse technologies, such as our Al advances, into the product lines, while developing new concepts for the future of the cloud. On the Mission Engineering team in SMT, he developed the Azure Space and Spectrum team, as well as the strategic modeling and simulation team, which includes silicon cloud design.

Prior to Microsoft, he was the director of the Microsystems Technology Office (MTO) for the Defense Advanced Research Projects Agency (DARPA) of the Department of Defense. Serving in this position, he focused the office on three key priorities important to national security. These thrusts included ensuring unfettered use of the electromagnetic spectrum, building an alternative business model for acquiring advanced DoD electronics that feature built-in trust, and developing circuit architectures for next-generation machine learning. MTO creates the MEMS, photonic, and electronic components needed to gracefully bridge the divide between the physical world in which we live and the digital realm where our information resides. Under Dr. Chappell's leadership, MTO developed the basic underpinnings of computation and sensing needed for an effective, information-driven society.

Prior to his work in government, Dr. Chappell was a professor at Purdue University specializing in electromagnetics. Dr. Chappell received his BS, MS, and PhD degrees in Electrical Engineering, all from the University of Michigan.

### **KEYNOTE PRESENTATIONS** continued

MICHAELA BLOTT SENIOR FELLOW, AMD RESEARCH

### **Enabling the Al Revolution**

Tuesday, June 24 | 8:45 AM - 10:00 AM

The hype surrounding AI has reached unprecedented levels, with governments and industries engaged in an arm's race towards Artificial General Intelligence. As AI permeates every aspect of our lives, from smart sensors and hearing aids to automotive, robotics, and high-energy particle physics, we face a diverse range of challenges that extend far beyond the widely discussed performance scalability and sustainability.

These challenges include demanding requirements such as nanosecond latency, tiny footprints, functional safety, and a high degree of customization.

This talk provides insights into the broad emerging spectrum of Al applications and discusses our latest research demonstrating how these challenges, ranging from bag tagging to 6G, can be addressed through silicon diversity, agile Al stacks and innovative solutions.

**ABOUT:** Dr. Michaela Blott is a Senior Fellow at AMD Research. She heads a team of international scientists driving groundbreaking research into AI, from robotics to computer architectures, model optimizations and green AI.

Her journey includes a Ph.D. from Trinity College Dublin and a Master's degree from the University of Kaiserslautern, Germany, and brings over 25+ years of experience in leading-edge AI, computer architecture and advanced FPGA design, in research institutions (ETH Zurich and Bell Labs) and development organizations.

She is highly active in the research community as industrial advisor to numerous EU projects and research centres, serves on technical program committees and her contributions to the field were further recognized through multiple Women in Tech Awards.

### **KEYNOTE PRESENTATIONS** continued

**JASON CONG**

VOLGENAU CHAIR FOR ENGINEERING EXCELLENCE PROFESSOR, UCLA COMPUTER SCIENCE DEPARTMENT

## Democratize Chip Design with Deep Learning and Automated Code Transformation

Wednesday, June 25 | 8:45 AM - 10:00 AM

In the past six decades, electronic design automation (EDA) has done a remarkable job to improve the productivity of hardware designers. I would like to argue that the next phase of EDA is to enable many software programmers to design their own chips or accelerators for a wide range of applications for better performance and energy efficiency, which is much needed as we are approaching the end of Moore's Law scaling. In this talk, I shall present our effort towards this goal. Coupled with our multi-decade research high-level synthesis (HLS), we developed and integrated multiple deep learning techniques, such as graph neural networks (GNNs) and large language models (LLMs), cross-modality learning, active learning with cross-entropy minimization, hierarchical mixture of expert modeling, and agent-based design space exploration. For regular structures, such as systolic arrays, stencil computation, or even more general affine programs used almost all deep learning kernel, we can also use mathematical programming to achieve automated code transformation. Combining these techniques, we show very promising results of mapping software code to high-quality silicon implementations.

**ABOUT:** Jason Cong is the Volgenau Chair for Engineering Excellence Professor at the UCLA Computer Science Department (and a former department chair), with joint appointment from the Electrical and Computer Engineering Department. He is the director of Center for Domain-Specific Computing (CDSC) and the director of VLSI Architecture, Synthesis, and Technology (VAST) Laboratory. Dr. Cong's research interests include novel architectures and compilation for customizable computing, synthesis of VLSI circuits and systems, and quantum computing. He has over 500 publications in these areas, including 19 best paper awards, and 4 papers in the FPGA and Reconfigurable Computing Hall of Fame. He and his former students co-founded AutoESL, which developed the most widely used high-level synthesis tool for FPGAs (renamed to Vivado HLS and Vitis HLS after Xilinx's acquisition). He is member of the National Academy of Engineering, the American Academy of Arts and Sciences, and a Fellow of ACM, IEEE, and the National Academy of Inventors. He is recipient of the SIA University Research Award, the EDAA Achievement Award, the IEEE Robert N. Noyce Medal for "fundamental contributions to electronic design automation and FPGA design methods", and the Phil Kaufman Award for "sustained fundamental contributions FPGA design automation technology, from circuit to system levels, with widespread industrial impact.

### SKYTALK PRESENTATIONS

**MOHAMED AWAD**

SENIOR VICE PRESIDENT AND GENERAL MANAGER, INFRASTRUCTURE LINE OF BUSINESS, ARM

### The Al Imperative: What Will We Make of This Moment?

Sunday, June 22 | 5:00 PM - 6:00 PM

**ABOUT:** Mohamed Awad leads the infrastructure line of business at Arm where he is responsible for leveraging Neoverse's class-leading performance per watt to accelerate Arm's growth across Cloud, HPC, 5G, and the Edge. Previously, Mohamed led Arm's IoT line of business.

Prior to joining Arm, Mohamed spent 10 years in various leadership roles at Broadcom, including establishing the Mixed Signal Asic Products division and building its security and mobile payments business. Before Broadcom, Mohamed served in various leadership roles at Ember Corporation, Lucent Technologies, Nortel Networks, and Avici Systems.

Mohamed has been named inventor or co-inventor on multiple patents throughout his career and holds a BS in Computer Science, from the University of Massachusetts.

JEFF WITTICH

CHIEF PRODUCT OFFICER, AMPERE

## Al's Growing Demands: How Artificial Intelligence is Redefining Semiconductor Innovation

Monday, June 23 | 1:00 PM - 1:45 PM | DAC Pavilion, Level 2 Exhibit Hall

The rapid evolution of artificial intelligence is fundamentally reshaping the semiconductor industry. All workloads demand unprecedented computational power. At the same time, the explosive growth of All inference is driving energy demands to new heights, forcing the industry to rethink power efficiency at every level – from silicon design to data-center scale optimization. This talk will explore how the demands of All are reshaping semiconductor innovation, the balance between performance and efficiency, and the advancements that are needed in silicon engineering to power this new era of computing.

**ABOUT:** Jeff Wittich is the Chief Product Officer at Ampere. Jeff has extensive leadership experience in the semiconductor industry in roles ranging from product and process development to business strategy to marketing. Prior to joining Ampere, he worked at Intel for 15 years in a variety of positions throughout the company. Most recently, he was responsible for the Cloud Service Provider Platform business, driving global market reach, product customization, and ultimately defining the products and platforms being used across the cloud worldwide. While at Intel, Jeff also led a product development team responsible for 5 generations of Xeon processors. He received an Intel Achievement Award for his work in developing the Custom CPU program.

Jeff has an MS in Electrical and Computer Engineering from the University of California, Santa Barbara, and a BS in Electrical Engineering from the University of Notre Dame.

### SKYTALK PRESENTATIONS continued

#### DR. MARK TEHRANIPOOR

CHAIR, ECE DEPARTMENT, UNIVERSITY OF FLORIDA, AND CO-FOUNDER, CASPIA TECHNOLOGIES

### **New Innovation Frontier with Large Language Models for SoC Security**

Tuesday, June 24 | 1:00 PM - 1:45 PM | DAC Pavilion, Level 2 Exhibit Hall

As complex SoCs become prevalent in virtually all systems, these devices also present a primary attack surface. The risks of cyberattacks are real, and Al is making them more sophisticated. As we also deploy Al into the SoC design process, it is imperative that secure design practices are incorporated as well.

Existing security solutions are inadequate to provide effective verification of complex SoC designs due to their limitations in scalability, comprehensiveness, and adaptability. Large Language Models (LLMs) are celebrated for their remarkable success in natural language understanding, advanced reasoning, and program synthesis tasks.

Recognizing this opportunity, we propose leveraging the emergent capabilities of Generative Pre-trained Transformers (GPTs) to address the existing gaps in SoC security, aiming for a more efficient, scalable, and adaptable methodology. In this presentation we offer an in-depth analysis of existing work, showcasing achievements, prospects, and challenges of employing LLMs in SoC security design and verification tasks.

**ABOUT:** Mark M. Tehranipoor is the Intel Charles E. Young Preeminence Endowed Professor in Cybersecurity at the Department of Electrical and Computer Engineering at the University of Florida. His current research projects include hardware security and trust, electronics supply chain security, IoT security, counterfeit IC detection and prevention, and reliable systems design. He has three patents and has published eight books, 11 book chapters and 350 papers. His projects are sponsored by both the industry (Texas Instruments, Freescale, Comcast, Honeywell, LSI, Mentor Graphics, Juniper, R3Logic, Cisco, Qualcomm, MediaTeck) and the government (NSF, ARO, MDA, DOD, AFOSR, DOE). He is a golden core member of IEEE.

### SKYTALK PRESENTATIONS continued

## SERGE NICOLEAU GROUP VICE-PRESIDENT OF TECHNOLOGY, STMICROELECTRONICS

### Al Booster for R&D, Edge Computing, Chiplets, and Sustainability

Wednesday, June 25 | 1:00 PM - 1:45 PM | DAC Pavilion, Level 2 Exhibit Hall

Artificial Intelligence (AI) is transforming Research and Development (R&D) by accelerating discovery, optimizing resources, and enhancing decision-making. Edge AI, which processes data closer to its source, reduces latency and energy consumption, promoting sustainability. Chiplet technology, involving smaller integrated circuits combined into larger systems, offers improved performance, scalability, and cost-efficiency. STMicroelectronics is exploring chiplets to advance semiconductor solutions. Amidst climate change, STMicroelectronics is committed to sustainable technologies and responsible products that support decarbonization and digitalization. Integrating AI into R&D, deploying Edge AI, and utilizing chiplets, while addressing sustainability, forms a comprehensive strategy for future advancements, ensuring technological progress and environmental responsibility.

**ABOUT:** Since 2024, Serge Nicoleau has served as Group Vice-President of Technology at STMicroelectronics, where he is responsible for defining, implementing, and driving the R&D governance of Digital and BCD technologies.

He began his career at STMicroelectronics in 1998, focusing on manufacturing management at the 200mm Crolles fab near Grenoble. Over the years, Serge has held various positions in manufacturing, process engineering, and equipment engineering. In 2004, he joined the Crolles 300mm fab as part of the Crolles2 Alliance between STMicroelectronics, Motorola/Freescale, and Philips/NXP. By 2007, he was promoted to Director of Industrial Technologies, and in 2012, he expanded his responsibilities as Deputy Director of Operations for both the Crolles 200mm and 300mm fabs.

In this role, he tackled the industrial challenges of Automotive and IoT products, working with technologies ranging from 0.5µm to 28nm critical dimensions, including their various variants and options. In 2018, Serge was involved in the new STMicroelectronics 300mm fab program in Agrate, Italy, supporting Smart Power, Analog Mixed Signal, and eNVM products.

In 2020, he assumed the role of General Manager of the Technology & Design Platforms organization, overseeing digital technologies, fast analog technologies, embedded memories, and optical sensors. This organization includes teams in France and India, focusing on the digital products of STMicroelectronics.

Serge Nicoleau holds an Engineering Degree from the Ecole Polytechnique (Paris), a master's degree in Theoretical Physics from the Ecole Normale Supérieure (Lyon), and a PhD in Particle Physics.

#### TECHTALK PRESENTATIONS

**AMIT GUPTA**VICE PRESIDENT & GM, CUSTOM

IC & SIEMENS EDA AI

DR. JOHN LINFORD HEAD OF PRODUCT, CAE/EDA, NVIDIA

### **Unlocking the Power of Al in EDA**

Monday, June 23 | 11:15 AM - 12:00 PM | DAC Pavilion, Level 2 Exhibit Hall

The semiconductor industry is experiencing unprecedented growth, and this growth comes with significant challenges—more design starts, rising design complexities, shorter time-to-market, and a shrinking talent pool. To address these challenges, semiconductor companies are turning to Al-powered EDA solutions. While mainstream Al & GenAl technologies have seen rapid consumer adoption, adapting these Al technologies for EDA use cases is not straightforward due to stringent quality requirements for semiconductor design.

Ideally, EDA AI solutions that provide productivity boosts to chip designers and engineers should (a) seamlessly analyze design and verification data, (b) optimize complex processes, and (c) generate better designs. Across these functional areas, we will discuss illustrative ML, GenAI, and Agentic approaches. Additionally, we will also discuss the challenges associated with AI adoption, including data availability, model interpretability, and computational demands.

Further, we will discuss the grand vision of having a purpose-built centralized EDA AI platform. Such a platform framework can be very powerful by combining sophisticated foundational models or even IC domain-specific foundational models with a multimodal data lake to bring GenAl capabilities to push the boundaries of semiconductor innovation, paving the way for more efficient, scalable, and intelligent design processes.

Join us to explore the capabilities of EDA AI and see what the future holds!

**ABOUT:** Amit Gupta is a technology executive and serial entrepreneur with over two decades of leadership in semiconductor design automation and Al innovation.

At Siemens EDA, Amit leads the Custom IC division and spearheads Al initiatives across the organization. Under his direction, the team develops cutting-edge Al technologies for the Siemens EDA portfolio, and solutions for variation-aware custom IC design, library characterization, IP validation, simulation, schematic capture, and layout—products that power the chips found in today's most advanced electronic devices.

A proven entrepreneur, Amit founded Solido Design Automation in 2005, and as President & CEO built it into the market leader for Al-based semiconductor design tools before its successful acquisition by Siemens in 2017. Previously, he founded and became President & CEO of Analog Design Automation (1999), which pioneered breakthroughs in circuit design automation and was acquired by Synopsys in 2004.

Amit holds dual degrees in Electrical Engineering and Computer Science with Great Distinction from the University of Saskatchewan.

ABOUT: Dr. John Linford leads NVIDIA's CAE/EDA product team. John's experience spans high-performance physical simulation,

extreme-scale software optimization, software performance analysis and projection, and pre-silicon simulation and design. Before NVIDIA, John worked at Arm Ltd. where he helped develop the Arm software ecosystem for cloud and HPC. John is based in Austin, TX.

### TECHTALK PRESENTATIONS continued

**WILLIAM WANG**FOUNDER AND CEO, CHIPAGENTS

## **Beyond Automation: How Agentic AI is Reinventing Chip Design and Verification**

Wednesday, June 25 | 11:15 AM - 12:00 PM | DAC Pavilion, Level 2 Exhibit Hall

Semiconductor innovation is at a critical juncture, demanding next-generational methods to overcome rising complexities, shorter design cycles, and intense competitive pressures. Traditional EDA tools are constrained by manual processes and limited intelligence, but what if we could transcend these limitations?

Enter Al Agents—the Al solution leveraging large language models and advanced algorithms to continue to improve themselves. In this talk, Prof. William Wang, Founder & CEO of ChipAgents, will introduce how Al agents go beyond traditional EDA automation, embedding agentic intelligence capable of independently handling hardware modeling, constraint-solving, automated debugging, testbench generation, and even proactive design optimization. Highlights include Use Cases, Scalability & Reliability: Case studies illustrating substantial productivity improvements, enhanced design quality, and accelerated time-to-market achieved by leading semiconductor enterprises deploying Al Agents. Al Agents in Action: Real-world scenarios demonstrating how Al agents autonomously identify critical bugs, optimize RTL designs, and significantly shorten verification cycles.

**ABOUT:** William Wang is an internationally recognized pioneer in artificial intelligence and the visionary Founder and CEO behind ChipAgents. He's also Duncan and Suzanne Mellichamp Endowed Chair Professor in Al and Design at UC Santa Barbara. His pioneering research has earned numerous prestigious accolades, including the IEEE Laplace Award, NSF CAREER Award, DARPA Young Faculty Award, the Karen Sparck Jones Award, and IEEE Al's 10 to Watch. William's vision drives ChipAgents' mission to transform semiconductor design through intelligent, agentic Al systems.

### ANALYST PRESENTATIONS

**DYLAN PATEL**CHIEF ANALYST, SEMIANALYSIS

### **Accelerator Package and System Design For The Al Era**

Monday, June 23 | 10:15 AM - 11:00 AM | DAC Pavilion, Level 2 Exhibit Hall

This session will discuss the design of accelerator packages and systems tailored for the AI era, addressing the need for improved performance, scalability, and energy efficiency to support complex AI workloads.

**ABOUT:** Through Dylan's dedication and vision, he has grown SemiAnalysis from a solo venture into a highly respected semiconductor market research firm. Since 2020, Dylan has expanded the business into a cohesive, specialized team, with competitive analysis at its core. The company's success has laid the foundation for fully realizing this vision within its new business unit.

JAY VLEESCHHOUWER SENIOR INDUSTRY ANALYST COVERING ENGINEERING AND ENTERPRISE SOFTWARE, GRIFFIN SECURITIES

### **A View from Wall Street**

Tuesday, June 24 | 10:15 AM - 11:00 AM | DAC Pavilion, Level 2 Exhibit Hall

We will examine the financial performance and key business metrics of the EDA industry through 2024, the further consolidation of EDA (the combination of Synopsys-Ansys), as well as the material technical and market trends and requirements that have influenced EDA business performance and strategies. Among the trends, we will again examine the progression of semiconductor R&D spending and how the market values of the publicly-held EDA companies have evolved. Lastly, we will provide our updated financial projections for the EDA industry for 2025 and 2026.

**ABOUT:** Mr. Vleeschhouwer has over four decades of research experience. He is a senior industry analyst covering Engineering and Enterprise Software, responsible for fundamental research of companies under coverage, including the regular publication of proprietary company and industry reports and detailed company and industry financial modeling. Principal industry reports include The Software Standard (software industry commentary, news, data, and analysis) and The State of EDA (quarterly in-depth review of Electronic Design Automation). He has appeared multiple times in the Institutional Investor "All-America Research Team" rankings and was ranked by Refinitiv Starmine Analyst Awards (U.S.) #1 in "top stock pickers" for software (2020). He has been regularly invited to present at software and other industry conferences, in addition to broadcast, print and online media appearances.

### **ANALYST PRESENTATIONS** continued

**STEVE GREENFIELD**GENERAL PARTNER, AUTOMOTIVE VENTURES

### The Future of Mobility

Wednesday, June 25 | 10:15 AM - 11:00 AM | DAC Pavilion, Level 2 Exhibit Hall

The way we transport humans and cargo is evolving at a pace not experienced since the beginning of the industrial revolution. This session will provide a glimpse into the future of mobility, including grand transportation, marine, aviation and space.

We'll not only discuss vehicle autonomy, electrification and connectivity, but explore how new technologies are impacting other modes of transportation.

**ABOUT:** Steve has more than 25 years of experience in the automotive technology space. He started his career in 1999 selling software to car dealers and has overseen more than \$1 billion in automotive technology acquisitions.

Steve served as TrueCar's Senior Vice President of Strategy and Business Development, and AutoTrader.com's Vice President of Product Management and Business Development, overseeing the acquisitions of vAuto, Kelley Blue Book, HomeNet Automotive, VinSolutions, and DealerScience.

Earlier in his career, Steve served as Manheim's Director of International Development, spearheading Manheim's overseas investments, including establishing new joint ventures in Dubai, Istanbul and Beijing.

He is the author of two books: "The Future of Automotive Retail," and "The Future of Mobility." He is also the author of the Weekly "Intel Report."

For fun, he likes to ride his three motorcycles on the racetrack and hang out with his twelve rescue cats.

### DAC AWARDS AND SCHOLARSHIPS

#### DAC

#### 2025 DAC UNDER-40 INNOVATORS AWARD

In recognition for technical contributions of notable impact in the field of design and automation of electronic circuits and systems

Tsung-Wei Huang, University of Wisconsin, Madison

Tushar Krishna, Georgia Institute of Technology

Xiaolin Xu, Norheastern University

Hajar Falahati, Barcelona Supercomputing Center

Souvik Kundu, Intel Corporation

### 2025 MARIE R. PISTILLI WOMEN IN ENGINEERING ACHIEVEMENT AWARD

For displaying equality, diversity, and acceptance while visibly helping to advance women in electronic design

**Marilyn Wolf**, Elmer E. Koch Professor of Engineering at the University of Nebraska, Lincoln

#### 2025 MOST INFLUENTIAL PAPER AWARD

Chisel: constructing hardware in a Scala embedded language, DAC'12

Jonathan Bachrach, UC Berkeley

Huy Vo, UC Berkeley

Brian Richards, UC Berkeley

Yunsup Lee, UC Berkeley

Andrew Waterman, UC Berkeley

Rimas Avižienis, UC Berkeley

John Wawrzynek, UC Berkeley

Krste Asanovic, UC Berkeley

#### 2025 BEST PAPER NOMINEES

INSTA: An Ultra-Fast, Differentiable, Statistical Static Timing Analysis Engine for Industrial Physical Design Applications

LVM-MO: A Large Vision Model Pioneer for Full-Chip Mask Optimization

GEM: GPU-Accelerated Emulator-Inspired RTL Simulation

CirSTAG: Circuit Stability Analysis on Graph-based Manifolds

PICK: An SRAM-based Processing-in-Memory Accelerator for

K-Nearest-Neighbor Search in Point Clouds

ZenLeak: Practical Last-Level Cache Side-Channel Attacks on AMD Zen Processors

BoolE: Exact Symbolic Reasoning via Boolean Equality Saturation

#### ACM/SIGDA

### ACM TODAES ROOKIE AUTHOR OF THE YEAR (RAY) AWARD

Enhanced Compiler Technology for Software-based Hardware Fault Detection

Davide Baroffio, Politecnico di Milano, Italy

#### 2025 ACM TODAES BEST PAPER AWARD

VeriGen: A Large Language Model for Verilog Code Generation

Shailja Thakur, New York University, USA

Baleegh Ahmad, New York University, USA

Hammond Pearce, University of New South Wales, Australia

Benjamin Tan, University of Calgary, CA

Brendan Dolan-Gavitt, New York University, USA

Ramesh Karri, New York University, USA

Siddharth Garg, New York University, USA

#### ACM SIGDA DISTINGUISHED SERVICE AWARD

Sharon Hu, University of Notre Dame

**Ulf Schlichtmann**, Technical University of Munich

#### SIGDA SERVICE AWARD

Yuan-Hao Chang, Academia Sinica

Preeti Ranjan Panda, Indian Institute of Technology Delhi

Frank Schirrmeister, Synopsys

Ziegenbein Dirk, Robert Bosch

### DAC AWARDS AND SCHOLARSHIPS continued

#### IEEE/CEDA

### 2024 PHIL KAUFMAN AWARD FOR DISTINGUISHED CONTRIBUTIONS TO EDA

For sustained fundamental contributions to Field-Programmable Gate Array (FPGA) design automation technology, from circuit to system levels, with widespread industrial impact.

Prof. Jason Cong, UCLA

#### **IEEE FELLOWS**

Umit Ogras, University of Wisconsin, Madison

Patrick Schaumont, Worcester Polytechnic Institute

Peilin Song, IBM Thomas J. Watson Research Center

Sheldon Tan, University of California, Riverside

### IEEE/ACM A RICHARD NEWTON TECHNICAL IMPACT AWARD IN ELECTRONIC DESIGN AUTOMATION

Luca Carloni, Columbia University

Kenneth L. McMillan, UT Austin

Alberto Sangiovanni-Vincentelli, UC Berkeley

#### IEEE CEDA OUTSTANDING SERVICE AWARD

For outstanding service to the EDA community as DAC General Chair in 2024

Vivek De, Intel

#### IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS DONALD O. PEDERSON BEST PAPER AWARD

SpikeSim: An End-to-End Compute-in-Memory Hardware Evaluation Tool for Benchmarking Spiking Neural Networks

Abhishek Moitra, Yale University

Abhiroop Bhattacharjee, Yale University

Runcong Kuang, Arizona State University

Gokul Krishnan, Meta Reality Labs

Yu Cao, Arizona State University

Priyadarshini Panda, Yale University

IEEE/CEDA also acknowledges the following awards presented to members of our community

IEEE GUSTAV ROBERT KIRCHOFF AWARD

Prof. Giovanni di Micheli, EPFL

IEEE JUN-ICHI NISHIZAWA MEDAL

Prof. Robert W. Dutton, Stanford University

IEEE JAMES H. MULLIGAN, JR. EDUCATION MEDAL

Prof. Jan Rabaey, UC Berkeley

IEEE COMPUTER SOCIETY EDWARD J. MCCLUSKEY

TECHNICAL ACHIEVEMENT AWARD

Prof. Hai (Helen) Li, Duke University

### DAC PAVILION SCHEDULE

The location for all events is:

DAC Pavilion | Level 2 Exhibit Hall - Booth #2237

#### Monday, June 23

10:15 AM - 11:00 AM

ACCELERATOR PACKAGE AND SYSTEM DESIGN FOR THE ALERA

Speaker: Dylan Patel, SemiAnalysis

11:15 AM - 12:00 PM

UNLOCKING THE POWER OF AI IN EDA

Speakers: Amit Gupta, Siemens; Dr. John Linford, Nvidia

1:00 PM - 1:45 PM

AI'S GROWING DEMANDS: HOW ARTIFICIAL INTELLIGENCE IS REDEFINING SEMICONDUCTOR INNOVATION

Speaker: Jeff Wittich, Ampere Computing

2:00 PM - 2:45 PM

GENERATIVE AI IN DESIGN & VERIFICATION: ARE WE HALLUCINATING OR INNOVATING?

Organizer: Joe Hupcey, Siemens

Moderator: Brian Bailey, Semiconductor Engineering Panelists: Alon Shtepel, Micron; Abhi Kolpekwar, Siemens

3:00 PM - 4:00 PM

**COOLEY'S DAC TROUBLEMAKER PANEL**

Moderator: John Cooley, Deepchip

Panelists: Mike Ellow, Siemens; Ravi Subramanian, Synopsys; Paul Cunningham, Cadence Design Systems, Inc.; Dean Drako, IC Manage; Prakash Narain, Real Intent; Sam Appleton, Ausdia

4:00 PM - 4:45 PM

DESIGN, DEVELOP, DOMINATE: THE CHIPS ACT'S ROLE IN SEMICONDUCTOR INNOVATION

Moderator: Nitin Dahad, EE Times Editor

Panelists: Vivek Prasad, NatCast; Nilesh Kamdar, Keysight Technologies; Saverio Fazzari, Senior Lead Engineer/ Engineering Fellow for Microelectronics

5:00 PM - 6:00 PM

**POSTER GLADIATOR BATTLE**

Tuesday, June 24

10:15 AM - 11:00 AM

**VIEW FROM WALL STREET**

Jay Vleeschhouwer, Griffin Securities

11:15 AM - 12:00 PM

EXPANDING THE TALENT POOL FOR IC DESIGN THROUGH EXPERIENTIAL LEARNING

Speaker: LaMar Hill, NY Design

1:00 PM - 1:45 PM

NEW INNOVATION FRONTIER WITH LARGE LANGUAGE MODELS FOR SOC SECURITY

Speaker: Mark Tehranipoor, University of Florida,

Caspia Technologies

2:00 PM - 2:45 PM

BREAKING THE DESIGN AUTOMATION MOLD: WILD AND CRAZY IDEAS FOR GLOBAL OPTMIZATION

Organizer: Nagesh Gupta, Ilmda.ai Moderator: Bernard Murphy, SemiWiki

Panelists: Gopal Iyer, Lattice Semiconductor; Vidya

Rajagopalan, Rivian; Rajesh Kashyap, Ericsson; Amit Dhir, PWC

3:00 PM - 3:45 PM

AI AND VLSI: A SYMBIOTIC REVOLUTION ENRICHING OUR LIVES AND SHAPING OUR FUTURE

Organizer: Mondira Pant, IEEE TCVLSI Chair - Intel Corporation;

Priya Panda, EEE TCVLSI Co-chair - Yale University

Moderator: Ramune Nagisetty, NatCast

Panelists: Manoj Selva, Intel Corporation; Sidney Tsai, IBM; Arijit RayChowdhury, Georgia Institute of Technology; Vijay Raghunathan, Purdue University; Rob Aitken, U.S.

Department of Commerce

4:00 PM - 4:45 PM

BUILDING SECURE CHIPS WITHOUT JEOPARDIZING DESIGN BUDGETS AND SCHEDULES

Organizer: Andreas Kuehlmann, Cycuity Moderator: Andreas Kuehlmann, Cycuity

Panelists: Rachana Maitra, Marvell; Mark Labbato, Booz Allen Hamilton; Vikram Khosa, ARM; Maurizio Paganini, Meta

5:00 PM - 6:00 PM

POSTER GLADIATOR BATTLE

WEDNESDAY, JUNE 25

10:15 AM - 11:00 AM

THE FUTURE OF MOBILITY

Speaker: Steve Greenfield, Automotive Ventures

11:15 AM - 12:00 PM

BEYOND AUTOMATION: HOW AGENTIC AI IS REINVENTING CHIP DESIGN AND VERIFICATION

Speakers: William Wang, ChipAgents

1:00 PM - 1:45 PM

AI BOOSTER FOR R&D, EDGE COMPUTING, CHIPLETS, AND SUSTAINABILITY

Speaker: Serge Nicoleau, STMicroelectronics

3:00 PM - 4:00 PM

**POSTER GLADIATOR BATTLE & AWARDS**

### EXHIBITOR FORUM SCHEDULE

The location for all events is:

DAC Exhibitor Forum | Level 1 Exhibit Hall - Booth #1343

### Monday, June 23

#### 10:30 AM - 11:00 AM

### TAMING THE WAVEFORM TSUNAMI: AGENTIC AI FOR SMARTER DEBUGGING

Speakers: Zackary Glazewski, ChipAgents.ai; William Wang, ChipAgents.ai

#### 11:15 AM - 11:45 AM

### THE GENERATIVE AI REVOLUTION IN SEMICONDUCTOR DEVELOPMENT

Speakers: Prashant Varshney, Microsoft; Richard Paw, Microsoft

#### 12:00 PM - 12:35 PM

### BEYOND BREAKING THE BOTTLENECK: SMART VERIFICATION FOR MODERN COMPLEXITY

Speakers: Abhi Kolpekwar, Siemens

#### 1:45 PM - 2:15 PM

### STATIC SIGN-OFF METHODOLOGIES: LIBERATING FUNCTIONAL VERIFICATION FROM BOOLEAN SHACKLES

Speakers: Prakash Narain, Real Intent; Kanad Chakraborty, Real Intent; Sanjay Thatte, Real Intent; Lisa Piper, Real Intent; Vikas Sachdeva, Real Intent

#### 2:30 PM - 3:00 PM

### MASTERING MODERN DATA MANAGEMENT: INSIGHTS AND CASE STUDIES

Speaker: Pedro Pires, Keysight Technologies

#### 3:30 PM - 4:00 PM

BUILDING TRUST IN GENAI FOR SEMICONDUCTOR DESIGN: ADDRESSING DATA PROVENANCE, QUALITY, AND TRACEABILITY CHALLENGES

Speaker: Vishal Moondhra, Perforce Software

#### 5:00 PM - 5:30 PM

## POWERING AI INFRASTRUCTURE WITH INNOVATIONS IN RELIABLE IN SYSTEM/ON-DIE MEMORY DESIGN AND CHARACTERIZATION

Speakers: Ehsan Rashid, Infosys; Chetan Kumar, Infosys; Shreekanth Sampigethaya, Infosys; Kamesh Akundi, Infosys

#### Tuesday, June 24

#### 10:30 AM - 11:00 AM

#### INTELLIGENT EXTRACTION OF ADVANCED IC PACKAGE

Speakers: Xiaoyan Xiong, Cadence Design Systems, Inc.; Yingxin Sun, Cadence Design Systems, Inc.; Jiyue Zhu, Cadence Design Systems, Inc.; Gang Kang, Cadence Design Systems, Inc.; Jian Liu, Cadence Design Systems, Inc.

#### 11:15 AM - 11:45 AM

### EDA IN THE CLOUD: OPTIMIZING CHIP DESIGN WORKFLOWS WITH GOOGLE CLOUD PLATFORM

Speaker: Sathya Narasimhan, Google

#### 12:00 PM - 12:30 PM

## LEVERAGING AI TO BOOST PRODUCTIVITY AND QUALITY OF RESULTS IN THE DIGITAL DESIGN CREATION FLOW

Speaker: Ankur Gupta, Siemens

#### 1:45 PM - 2:15 PM

### COVERAGENT: HOW AGENTIC AI IS REDEFINING FUNCTIONAL COVERAGE CLOSURE

Speakers: Mehir Arora, ChipAgents.ai; Zackary Glazewski, ChipAgents.ai; William Wang, ChipAgents.ai

#### 2:30 PM - 3:15 PM

#### THE RENAISSANCE OF EDA STARTUPS

Speakers: Moshe ZalcbergVeriest, Silicon Catalyst; Priyanka Mathikshara, Voltai; Kanu Gulati, Khosla Ventures; Brian Schechter, Primary Venture Partners; Vinod Kariat, Cadence Design Systems, Inc.

#### 3:30 PM - 4:00 PM

### ACCELERATING TAPEOUT BY MONTHS WITH COST-EFFECTIVE PER-MINUTE EDA CLOUD LICENSING

Speakers: Vikram Bhatia, Synopsys;

#### 4:15 PM - 4:45 PM

## INDUSTRY-LEADING 3D-IC MULTI-DIE SILICON COMPANIES DISCUSS THEIR MULTIPHYSICS CHALLENGES

Speakers: Murat Becer, Ansys; Sonia Leon, Intel Corporation; Prakhar Mathur, Nvidia; Nitin Navale, Advanced Micro Devices (AMD); Llius Paris, TSMC

#### 4:15 PM - 5:15 PM

### A CONFIGURABLE ECAD LIBRARY SOLUTION FOR ALL USERS

Speakers: Julie Liu, Palpilot International

### **EXHIBITOR FORUM SCHEDULE** continued

The location for all events is:

DAC Exhibitor Forum | Level 1 Exhibit Hall - Booth #1343

### Wednesday, June 25

10:30 AM - 11:00 AM

GENAI-POWERED CYBER-RESILIENT RTL FOR SECURE AND ROBUST SEMICONDUCTOR DEVICES

Speakers: Peter Levin, Amida Technology Solutions

11:15 AM - 11:45 AM

SIEMENS: ENGINEERING THE SEMICONDUCTOR

**DIGITAL THREAD**

Speakers: Vishal Moondhra, Perforce Software; Michael

Munsey, Siemens

1:45 PM - 2:15 PM

**DEEPPCB: TRANSFORMING PCB PLACE & ROUTE**

THROUGH REINFORCEMENT LEARNING

Speakers: Alain-Sam Cohen, InstaDeep

#### Program accurate as of June 17, 2025.

Locations listed for each speaker are representative of where they live, not where their corporate office is located.

### **FULL PROGRAM**

**Sunday, June 22, 2025**

POWERING THE FUTURE: MASTERING IEEE 2416 SYSTEM LEVEL POWER MODELING STANDARD FOR LOW-POWER AI AND BEYOND

Time: 9:00 AM - 12:30 PM Session Type: Half-day Tutorial

Topic Area(s): AI Room: 3006, Level 3

**Description:** This half-day tutorial will provide attendees with a comprehensive understanding of the IEEE 2416 standard, used for system level power modeling in the design and analysis of integrated circuits and systems. Through a combination of lectures, discussions, and handson exercises, participants will gain practical knowledge and skills necessary to implement and utilize the standard effectively. The workshop will highlight the pressing need for low-power design methodologies, particularly in cuttingedge fields like AI, where computational demands are high. By getting a clear understanding of the IEEE 2416 standard. attendees will be equipped to make decisions on how the standard can be incorporated into their design flow to deliver the efficiencies needed to build their cutting-edge low power designs. The presenters, who are experts from different industry segments (EDA, Foundry, SoC and IP) and academia will use the IEEE2416-2025 version of the standard that is being released at DAC 2025 to explain concepts presented in the workshop.

Organizer(s): Nagu Dhanwada, IBM, US; Leigh Anne Clevenger, Si2, Inc., US

**Speakers:** Daniel Cross, Cadence Design Systems, Inc., US; Rhett Davis, North Carolina State University, US; Eunju Hwang, Samsung, BE; Pritesh Johari, Qualcomm, US; Akil Sutton, IBM, US

#### **QUANTUM COMPUTING DESIGN AUTOMATION**

Time: 9:00 AM - 12:30 PM Session Type: Tutorial Topic Area(s): Design Room: 3004, Level 3

**Description:** This tutorial provides a comprehensive exploration of design automation for quantum computing, structured into three focused sections, each addressing critical challenges and advancements in the field. With quantum computing poised to revolutionize technology, the efficient design and optimization of quantum systems are

imperative for scaling, performance enhancement, as well as sustainability.

**Organizer(s):** Hanrui Wang, University of California, Los Angeles, US; Zhiding Liang, Rensselaer Polytechnic Institute, US

**Speakers:** Yiran Chen, Duke University; Weiwen Jiang, George Mason University; Siyuan Niu, Lawrence Berkeley National Lab; Daniel Tan, Harvard; Thomas W. Watts, HRL Labs

## THE 2ND INTERNATIONAL WORKSHOP ON DEEP LEARNING -- HARDWARE CO-DESIGN FOR GENERATIVE AI ACCELERATION

Time: 9:00 AM - 12:30 PM Session Type: Workshop

Topic Area(s): AI Room: 3003, Level 3

**Description:** In the rapidly evolving domain of computational technologies, the transformative impact of artificial intelligence (AI) continues to shape the future. DCgAA 2025 builds on the success of its inaugural edition by diving deeper into the frontier of deep learning (DL) and hardware co-design, with an amplified focus on real-world deployment challenges and next-generation innovations for generative AI applications. This second iteration emphasizes expanding the scope beyond foundational discussions, addressing emerging paradigms in generative AI, including multimodal fusion, real-time adaptive processing, and decentralized edge applications. Acknowledging the growing role of foundation models, diffusion models, and large-scale generative systems, this workshop prioritizes optimizing these technologies for sustainable scalability—balancing performance, energy efficiency, and accessibility across diverse computing environments such as edge devices, AR/VR platforms, and ubiquitous IoT systems. Through a blended format of keynotes, paper presentations, interactive discussions, and novel program additions, DCqAA 2025 seeks to redefine the boundaries of DL-hardware integration. By engaging thought leaders, researchers, and practitioners across academia and industry, this workshop promises to set new benchmarks for hardware-aware generative AI, driving innovation that is efficient, scalable, and impactful in the real world.

Organizer(s): Dongkuan Xu, North Carolina State University, US; Tinoosh Mohsenin, University of Maryland, Baltimore County, US; Caiwen Ding, University of Minnesota Twin Cities, US; Hua Wei, Arizona State University, US; Ang Li, University of Maryland, US; Peipei Zhou, Brown University, US; Yingyan (Celine) Lin, Georgia Institute of Technology, US; Yanzhi Wang, Northeastern University, US

## IN-MEMORY ARCHITECTURES AND COMPUTING APPLICATIONS WORKSHOP (IMACAW) - 4TH EDITION

Time: 9:00 AM - 12:30 PM Session Type: Workshop Topic Area(s): Design Room: 3002, Level 3

**Description:** Modern computer architectures and the device technologies used to manufacture them are facing significant challenges, limiting their ability to meet the performance demands of complex applications such as Big Data processing and Artificial Intelligence (AI). The In-Memory Architectures and Computing Applications Workshop (iMACAW) workshop seeks to provide a platform for discussing In-Memory Computing (IMC) as an alternative architectural approach and its potential applications. Adopting a cross-layer and cross-technology perspective, the workshop will cover state-of-the-art research utilizing various memory technologies, including SRAM, DRAM, FLASH, RRAM, PCM, MRAM, and FeFET. Additionally, the workshop aims to strengthen the IMC community and offer a comprehensive view of this emerging computing paradigm to design automation professionals. Attendees will have the opportunity to engage with invited speakers, who are pioneers in the field, learn from their expertise, ask questions, and participate in panel discussions.

**Organizer(s):** Deliang Fan, Arizona State University, US; Nima TaheriNejad, Heidelberg University, DE; Wantong Li, University of California, Riverside

### 3RD AI/CAD FOR HARDWARE SECURITY WORKSHOP (AICAD4SEC 2025)

Time: 9:00 AM - 5:00 PM Session Type: Workshop Topic Area(s): AI, Security Room: 3001, Level 3

**Description:** Security vulnerabilities in hardware designs are catastrophic as once fabricated, they are nearly impossible to patch. Modern SoCs (Systems-on-Chip) face threats like side-channel leakage, information leakage, access

control violations, and malicious functionality, jeopardizing the foundational integrity of SoCs. These vulnerabilities circumvent software-level defenses, creating urgent challenges for hardware security. Ensuring the security of hardware designs is challenging due to their huge complexity, aggressive time-to-markets, and the variety of attacks against hardware designs. Moreover, it is very costly for a design house to keep many security experts with indepth design knowledge with diverse security implications. So, the semiconductor industry looks for a set of metrics, reusable security solutions, and automatic computer-aideddesign (CAD) tools to aid analysis, identifying, root-causing, and mitigating SoC security problems.

Artificial Intelligence (AI) is revolutionizing the landscape of CAD, providing unprecedented opportunities to tackle these challenges. Al-driven tools have the potential to analyze complex SoC designs at multiple abstraction levels, automatically detect vulnerabilities, and even predict potential attack vectors. By leveraging advanced AI models, including large language models (LLMs) and machine learning algorithms, we can now accelerate the identification of root causes, assess risks, and recommend security countermeasures. The inclusion of AI in CAD/EDA for security addresses these issues in innovative ways, e.g., (1) Enhanced Vulnerability Detection, (2) Contextual Adaptability, and (3) Proactive Security.

Building on the resounding success of the 1st (inauguration) and 2nd CAD4Sec workshops, co-located with the DAC'59 (2022) and DAC'60 (2023), respectively, and drawing ~100 attendees each year, the 3rd iteration aims to embrace the transformative intersection of AI, CAD, and hardware security. Now rebranded as AICAD4Sec, this workshop aims to drive innovation at the nexus of Al-driven solutions and hardware design security. The ultimate vision of AICAD4Sec is to establish a cutting-edge platform that shows advancements and sets the roadmap for secure, Alenabled hardware design, specifically, (i) Engaging experts from industry leaders like Google, Microsoft, Synopsys, and ARM, alongside academia and government agencies such as DARPA and AFRL; (ii) Showcasing the latest breakthroughs in Al-enhanced CADs for security; (iii) Facilitating practical demonstrations of Al-driven solutions in hardware security by both industries/academia; and (iv) Hosting a dynamic panel discussion on the evolving role of Al, with a particular focus on large language models and their implications for secure SoC design.

Building on the foundation of its predecessors, the 3rd AICAD4Sec workshop will contain several technical talks on the scope of metrics and CAD as the following:

- CAD Tools for Side-Channel Vulnerability Assessment (Power, Timing, and Electromagnetic Leakage)

- Security-Oriented Equivalency Checking and Property Validation

- Fault Injection Analysis and Countermeasure Integration in CAD

- CAD for Secure Packaging and Heterogeneous Integration

- · Assessment of Physical Probing and Reverse Engineering Risks

- Al-Powered Tools for Pre-Silicon Vulnerability Mitigation and Countermeasure Suggestions

- Large Language Models for Security-Aware Design Automation

- ML-Enhanced Threat Detection Across Design Abstractions

- Al-Augmented Detection of Malicious Functionality in Hardware Designs

- Al-Enabled Security Verification for Emerging SoC Architectures

**Organizer(s):** Farimah Farahmandi, University of Florida; Hadi Mardani Kamali, University of Central Florida; Mark Tehranipoor, University of Florida

## WORKSHOP ON CHIPLET-BASED HETEROGENEOUS INTEGRATION AND CODESIGN (CHICO)

Time: 9:00 AM - 5:00 PM Topic Area(s): Design Session Type: Workshop Room: 3000, Level 3

Description: Contemporary microelectronic design is facing tremendous challenges in memory bandwidth, processing speed and power consumption. Although recent advances in monolithic design (e.g. near-memory and in-memory computing) help relieve some issues, the scaling trend is still lagging behind the ever-increasing demand of AI, HPC and other applications. In this context, technological innovations beyond a monolithic chip, such as 2.5D and 3D packaging at the macro and micro levels, are critical to enabling heterogeneous integration with various types of chiplets and bringing significant performance and cost benefits for future systems. Such a paradigm shift further drives new innovations on chiplet IPs, heterogeneous architectures and system mapping.

This workshop is designed to be a forum that is highly interactive, timely and informative, on the related topics:

- Roadmap and technology perspectives of heterogeneous integration

- IP definition for chiplets

- Signaling interface cross chiplets

- Network topology for data movement

- Design solutions for power delivery

- Thermal management

- Testing in a heterogeneous system

- · High-level synthesis for the chiplet system

- Architectural innovations

- Ecosystems of IPs and EDA tools

The format of the workshop will consist of multiple invited presentations from industry, academia, and government funding agencies. We will also organize a panel for discussions. Intended audience includes industry and academic researchers, funding agencies, IP providers, EDA tool vendors, and foundry engineers.

**Organizer(s):** Yu Cao, University of Minnesota, US; Puneet Gupta, University of California, Los Angeles, US

#### EVEN HIGHER-LEVEL SYNTHESIS: AN EXPLORATION OF AI HARDWARE ACCELERATORS USING HLS4ML

Time: 1:30 PM - 3:00 PM

Topic Area(s): AI Session Type: Tutorial Room: 3006, Level 3

**Description:** With the rise of artificial intelligence, the popularization of deep learning, and a constantly evolving industry, the demand for flexible and efficient tools has never been greater. As algorithms grow more complex, their runtime and energy consumption increase exponentially. Customized hardware accelerators, long used for specific mathematical operations, remain essential for managing modern applications' computational and power demands. Hardware accelerators can speed up complex computations by orders of magnitude, but their manual design and verification processes are often challenging and time-consuming.

High-Level Synthesis (HLS) provides a solution by transforming high-level algorithm descriptions, typically written in C or C++, into synthesizable RTL suitable for hardware implementation. This approach reduces development time for RTL engineers while offering flexibility beyond what traditional handwritten RTL can provide. We extended this capability to the machine learning domain with the open-source framework hls4ml, which allows neural networks trained in Python frameworks like Tensorflow or PyTorch to be synthesized into efficient hardware representations for the traditional FPGA and ASIC flows. This breakthrough addresses the growing need for reduced design turnaround and easy verification of ML hardware accelerators with low latency and power efficiency constraints.

During this tutorial, we will demonstrate how Python complements HLS by simplifying the ML design process, bridging the gap between software and hardware development. Attendees will explore how we translate neural networks modeled in Python into fixed-point C++ models suitable for HLS workflows. We will dive into strategies like Value-Range Analysis and Quantization-Aware Training, which optimize these designs for deployment and evaluate their accuracy, power consumption, and energy efficiency.

Organizer(s): Mathilde Karsenti, Siemens, US

Speakers: Cameron Villone, Siemens EDA, US; Giuseppe Di

Guglielmo, Fermilab, US

### INTRODUCTION TO FOUNDATION AI MODEL AND ITS EDA APPLICATIONS

Time: 1:30 PM - 5:00 PM

Topic Area(s): Al Session Type: Tutorial Room: 3004, Level 3

**Description:** The objectives of this tutorial are to provide a solid foundation in understanding large language models and their applications, equip participants with the trending Al knowledge to apply self-supervised learning techniques effectively in their own target applications, demonstrate the integration of multimodal data for enhanced Al capabilities, and discuss strategies to improve the efficiency of large-scale models. This tutorial content is designed for researchers, industry practitioners, and students interested in the latest advancements in Al model development and deployment. Our target audience may work in different backgrounds, including but not limited to: EDA researchers or engineers, especially those interested in AI for EDA; computer architecture researchers or engineers, especially those working on Al accelerator design; algorithm researchers or engineers, especially those working on Al algorithms, applications, and products. The tutorial will cover basic large language model (LLM) techniques, including transformer and RAG, self-supervised pretraining techniques, such as contrastive learning, multimodal representation learning, the efficiency of large foundation models, and foundation Al model's applications in EDA

Organizer(s): Xiaoxuan Yang, University of Virginia, US.

**Speakers:** Zhiyao Xie, Hong Kong University of Science and Technology (HKUST), HK; Wei Wen, Meta, US; Ang Li, The University of Maryland, College Park, US; Zhiyao Xie, Hong Kong University of Science and Technology (HKUST), CN

#### FIRST INTERNATIONAL WORKSHOP ON SYNERGIZING AI AND CIRCUIT-SYSTEM SIMULATION

Time: 1:30 PM - 5:00 PM Topic Area(s): Design Session Type: Workshop Room: 3003, Level 3

**Description:** Hardware tape-outs are prohibitively expensive and time-consuming, making circuit and system (CAS) simulators crucial for verifying designs efficiently and cost-effectively prior to fabrication. An extensive array of simulators exists today, tailored for various CAS applications, such as Verilog simulators for digital integrated circuits (ICs), SPICE-based simulators for analog ICs, Verilog-AMS simulators for mixed-signal systems, and electromagnetic simulators for high-frequency circuits and antennas. Despite decades of development and the high degree of maturity achieved by CAS simulators, the recent surge of artificial intelligence (AI) is rekindling renewed interest from both software and hardware perspectives. On the hardware front, the exceptional parallelism capabilities of GPUs can be harnessed to expedite CAS simulations, such as GPU-accelerated SPICE simulations and logic gate simulation. On the software side, deep learning (DL) algorithms are being seamlessly integrated into CAS simulators serving as surrogate models or providing initial guesses, to reduce computational workloads and improve efficiency. Conversely, the principles of CAS simulation are catalyzing novel Al models. One prominent example is the use of ordinary differential equations (ODEs), which have long been a cornerstone of time-domain analog circuit simulations in SPICE, with the adjoint method used for gradient computations. In the DL community, these techniques have evolved into Neural ODEs, a class of models that parameterize ODE dynamics using neural networks. Neural ODEs have proven especially effective for time-series forecasting and are closely linked to the development of generative diffusion models. Similarly, state-space models (SSMs), once the bedrock of linear time-invariant systems, now underpin architectures such as Mamba, designed for efficient natural language processing. Another notable adaptation of classical circuit principles in modern AI is Kirchhoff's current law (KCL), which has been leveraged to construct analog neural networks, such as memristor crossbar arrays and KirchhoffNet. Furthermore, Fourier transforms, widely used in frequency-domain CAS simulations for signal processing, have been reimagined as neural operators. This adaptation has led to breakthroughs in Al-driven scientific applications, such as weather forecasting.

The similarities between CAS simulation and Al are profound, yet no dedicated platform exists for researchers, engineers, and practitioners to discuss this interdisciplinary topic. Recognizing this critical need, the First International Workshop on Synergizing Al and Circuit-System Simulation aims to bring together experts to explore innovative methodologies that leverage the synergies between these fields. The workshop will provide a platform to discuss recent advancements and foster interdisciplinary collaboration.

Organizer(s): Zhengqi Gao, Massachusetts Institute of Technology, US; Duane Boning, MIT, US; Zhou Jin, Super Scientific Software Laboratory, Dept. of CST, CN University of Petroleum-Beijing, CN; Yanqing Zhang, Nvidia, US; Haoxing Ren, Nvidia Corporation, US; Yiran Chen, Duke University, US; Ron Rohrer, CMU, US

## NSF WORKSHOP ON HARDWARE ATTACK ARTIFACTS, ANALYSIS, AND METRICS (WHAAAM)

Time: 1:30 PM - 5:00 PM Topic Area(s): Security Session Type: Workshop Room: 3002, Level 3

Description: The Workshop on Hardware Attack Artifacts, Analysis, and Metrics (WHAAAM) aims to promote open and practical contributions that improve our ability to reason about offensive hardware security. Over the past decade, we've observed the repeated discovery of realworld hardware vulnerabilities. No longer a theoretical exercise, hardware attacks are developed by multinational corporations and nation states with devastating consequences. Responses from both academia, industry, and government agencies has grown as a result. However, we still fall-short in our ability to defend against creative malicious actors. This is in part due to an existing gap between academic threat modelling and PoCs versus end-to-end attacks. WHAAM seeks to bridge this gap in the hardware security research community, by seeking open and artifactdriven submissions that that grows our understanding of practical attacker capabilities, as well as robust responses based on empirical root-cause analysis and quantitative metrics. Importantly, as opposed to competition-based hardware security events (Hack@DAC, IEEE HOST) that have limited focus, WHAAAM encourages a diverse and creative outlet for student researchers to demonstrate a range of cutting-edge work in a hands-on environment.

Organizer(s): Dean Sullivan, University of New Hampshire, US; Vincent Immler, Oregon State University, US

### EMERGING TECHNOLOGY APPLICATIONS ON PERSONALIZED EDGE LLMS

Time: 3:30 PM - 5:00 PM

Topic Area(s): Al Session Type: Tutorial Room: 3006, Level 3

Description: Edge-based Large Language Models (edge LLMs) can preserve the promising abilities of LLM while ensuring user data privacy. Additionally, edge LLMs can be utilized in various fields without internet connectivity constraints. However, edge LLMs face significant challenges in training, deployment, and inference. Limitations in memory storage, computational power, and data I/O operations can hinder the deployment of advanced LLMs on edge devices. These constraints often result in poor performance in customization, real-time user interaction, and adaptation to novel situations. Traditional acceleration methods, primarily designed for advanced computation platforms, may not be optimal for all types of edge devices. As a complementary solution, Compute-in-Memory (CiM) architectures based on emerging non-volatile memory (NVM) devices offer promising opportunities. These architectures, having demonstrated numerous advantages in traditional neural networks, can help overcome the computational memory bottleneck of edge devices and reduce competition for core computational resources. Through the introduction of software-hardware co-design and co-optimization methods, NVCiM can significantly enhance edge LLM performance in resourcelimited environments. Moreover, NVCiM-based edge LLM systems are more cost-effective compared to LLMs running on high-performance computing devices. This makes them suitable for various personalized applications, particularly in healthcare and medical fields.

Organizer(s): Ismail Bustany, AMD, US

Speakers: Yiyu Shi, University of Notre Dame, US; Jinjun

Xiong, University at Buffalo, US

### SUNDAY WORK-IN-PROGRESS POSTER RECEPTION

Time: 6:00 PM - 7:00 PM

Session Type: Work-in-Progress Poster

Room: Level 3 Lobby

3D-IC STACKING AND FLOORPLAN DESIGN

METHODOLOGY THROUGH ML-BASED

PRE-TRAINED MODEL AND PRACTICAL MACRO

PLACEMENT FRAMEWORK FOR PERFORMANCE AND

THERMAL CO-OPTIMIZATION

Yu-Wei Tseng, Po-Hsiang Huang, Wei-Yi Willy Hu, Intel, US

### A FAST AND ACCURATE THERMAL SOLVER FOR CHIP THERMAL THROTTLING ANALYSIS

Shinyu Shiau, Sainan Lu, Stimit Shah, Xin Ai, Yun Dai, Cadence Design Systems, Inc., US

#### A GRAPH-BASED APPROACH FOR OPTIMIZING PIN ACCESS IN NANOSHEET FET STANDARD CELL LIBRARY SYNTHESIS

Meng-Yu Shih, Yih-Lang Li, National Yang Ming Chiao Tung University, TW

## A RETINA-INSPIRED PATHWAY TO REAL-TIME MOTION PREDICTION INSIDE IMAGE SENSORS FOR EXTREME-EDGE INTELLIGENCE

Subhradip Chakraborty, Md Kaiser, Akhilesh Jaiswal, University of Wisconsin Madison, US; Shay Snyder, Maryam Parsa, George Mason University, US; Gregory Schwartz, Northwestern University, US

#### A SCALABLE TWO-STEP APPROACH TO OPTIMIZE DATA AND ENERGY MIGRATIONS IN MINI DATA CENTERS FOR CARBON-NEUTRAL COMPUTING

Kazuki Okazawa, Hiroki Nishikawa, Dafang Zhao, Ittetsu Taniguchi, Takao Onoye, Osaka University, JP; Marcos da Silva, Independent Researcher, FR; Abdoulaye Gamatie, LIRMM, FR

#### ACCELERATING CLUSTERING ALGORITHMS FOR LARGE-SCALE DATASETS VIA COLLABORATIVE GPU AND CXL-MEMORY ARCHITECTURE

Taehyung Park, Hyuk-Jae Lee, Seoul National University, KR; Chae Eun Rhee, Hanyang University, KR

### ACCELERATING DEVICE LEVEL SYNTHESIS OF BINARIZED CONVOLUTIONAL NEURAL NETWORKS

Francisco Andreo-Oliver, Gines Domenech-Asensi, Ramon Ruiz-Merino, Universidad Politecnica de Cartagena, ES; Jose Diaz-Madrid, Centro Universitario de la Defensa - UPCT, ES

### ADAMAP: ADAPTIVE HARDWARE MAPPING FOR MODEL COMPRESSION USING LOW-RANK DECOMPOSITION

Priyansh Bhatnagar, Rishabh Kumar, Pranav Raj, Mingu Kang, University of California, San Diego, US

## ADORA: AN ARITHMETIC AND DYNAMIC OPERATION RECONFIGURABLE ACCELERATOR USING IN-MEMORY LOOK-UP TABLES

Stefan Maczynski, Mark Indovina, Sathwika Bavikadi, Amlan Ganguly, Rochester Institute of Technology, US; Purab Sutradhar, Boise State University, US; Sai Manoj Pudukotai Dinakarrao, George Mason University, US

### AI-ENABLED EFFICIENT EXTRACTION OF ENTIRE ADVANCED IC PACKAGE

Xiaoyan Xiong, Yingxin Sun, Jiyue Zhu, Gang Kang, Jian Liu, Cadence Design Systems, Inc., US

## ALPHASPARSETENSOR: DISCOVERING FASTER SPARSE MATRIX MULTIPLICATION ALGORITHMS ON GPU FOR LLM INFERENCE

Xuanzheng Wang, Shuo Miao, Zihan Zhu, Peng Qu, Youhui Zhang, Tsinghua Univ., CN

## AN ADVANCED WAIT-FREE PROTOCOL FOR DATA COMMUNICATION AND CONSISTENCY IN MULTI-CORE REAL-TIME EMBEDDED SYSTEMS

Dong Li, Sen Wang, Adhip Shukla, Haibo Zeng, Virginia Tech, US; Yuchen Zhou, Khaja Shazzad, General Motors, US

### APPROXIMATION-BASED INTER-PE COMMUNICATION-FREE IMAGE FILTERING FOR COMMODITY PIM

Chan Lee, Shinnung Jeong, Heelim Choi, Jaeho Lee, Haeeun Jeong, Hoyun Youm, Ju Min Lee, Hanjun Kim, Yonsei University, KR

## AUTOMATED HARDWARE-MAPPING CO-DESIGN FOR NEURAL NETWORK ACCELERATION WITH SINGLE-STEP REINFORCEMENT LEARNING

Yifeng Xiao, University of Southern California, US; Yurong Xu, Ning Yan, Masood Mortazavi, Futurewei, US; Pierluigi Nuzzo, University of California, Berkeley, US

#### **AUTOMATING RTL GENERATION USING AGENTIC LLMS**

Athmanarayanan Lakshmi Narayanan, Mahesh Subedar, Omesh Tickoo, Intel, US

### AUTOMOTIVE REMOTE DIRECT MEMORY ACCESS (ARDMA) FOR SOFTWARE DEFINED VEHICLE (SDV)

Nithya Somanath, Bhagyashri Katti, Zachary Steigerwald, Khaja Shazzad, Markus Jochim, Yuchen Zhou, Steve DiBella, General Motors, US

#### BANK-SPLIT PIM: ENABLING CONCURRENT PIM AND MEMORY OPERATIONS FOR LLM INFERENCE IN HETEROGENEOUS SYSTEMS

Hyeongjun Cho, Yoonho Jang, Seokin Hong, Sungkyunkwan University, KR

#### **BEYOND VERILOG: AGENTS FOR EMERGING HDLS**

Farzaneh Rabiei Kashanaki, Mark Zakharov, Jose Renau, University of California, Santa Cruz, US

### BLAQSMITH: RESOLVING TWO-QUBIT GATE COUNT EXPLOSION IN T-COUNT-OPTIMIZED QUANTUM CIRCUITS

Mu-Te Lau, Hsiang-Chun Yang, Hsin-Yu Chen, Chung-Yang (Ric) Huang, National Taiwan University, TW

Special **Panel** Tutorial Workshop; **Exhibitor DAC Pavilion** TechTalk Keynotes and Research **Engineering** Hands-on Panel: Analyst **SKYTalk** Sessions Session Forum Visionary Talks Track **Tutorial** Review

### SUNDAY WORK-IN-PROGRESS POSTER RECEPTION (continued)

### CARBONSET: A DATASET TO ANALYZE TRENDS AND BENCHMARK THE SUSTAINABILITY OF CPUS AND GPUS

Jiajun HU, Chetan Choppali Sudarshan, Maxwell Clifford, Vidya A. Chhabria, Aman Arora, Arizona State University, US

### CIS: IN-STORAGE COMPRESSION FOR IMPROVING READ PERFORMANCE OF NAND FLASH-BASED SSDS

Minjin Park, Minkyu Choi, Seongwook Kim, Junbum Park, Joonseong Hwang, Seokin Hong, Sungkyunkwan University, KR

## COMBINING PHYSICS-INFORMED AND DATA-DRIVEN LEARNING FOR EFFICIENT MODELING OF MEMRISTIVE DEVICES

Zihan Zhang, Marco Donato, Tufts University, US

#### DAEDALUS: A FLOORPLANNING STRATEGY FOR NEXT-GENERATION 3D CHIPLET INTEGRATION

Sebastiano Gaiardelli, Michele Lora, Franco Fummi, University of Verona, IT; Marco Cignarella, Anna Fontanelli, Francesco Rossi, Michele Taliercio, Monozukuri S.p.A, IT

### DEEP CO-DESIGN OF A 7.461 TOPS/W/MM^(2) CGRA FOR EDGE-BASED PERCEPTION APPLICATIONS

Rohit Prasad, Pascal Aubry, Tiana Rakotovao, Kods Trabelsi, CEA, FR

#### DESIGN GUIDELINES OF SUCCINCT PULSE GENERATORS FOR SCALABLE SUPERCONDUCTING QUBIT CONTROLLERS